# SL6140

# 400MHz Wideband AGC Amplifier

DS2159

Issue no 5.0 July 1999

### Features

- 400MHz Bandwidth (R<sub>1</sub> =50Ω)

- High voltage Gain 45dB ( $R_1 = 1k\Omega$ )

- 70dB Gain Control Range

- High Output Level at Low Gain

- Surface Mount Plastic Package

- Low Cost

# Applications

- RF/IF Amplifier

- High Gain Mixers

- Video Amplifiers

# Description

The SL6140 is an integrated broadband AGC amplifier, designed on an advanced bipolar process. The amplifier provides over 15dB of linear gain into  $50\Omega$  at 400MHz. Gain control is also provided with over 70dB of dynamic range. The SL6140 offers over 45dB of voltage gain with an R<sub>1</sub> of 1k $\Omega$ .

# Ordering Information

SL6140/NA/MP Industrial temperature range miniature plastic package

SL6140/NA/MPTC Tape and Reel

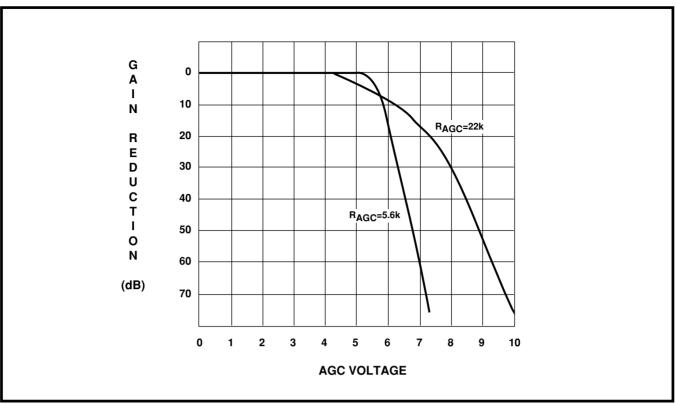

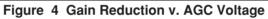

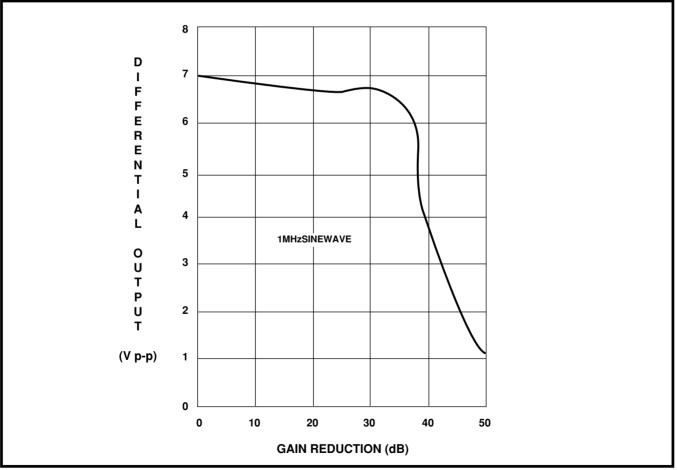

The SL6140 (Figure 3) is a high gain amplifier with an AGC control capable of reducing the gain of the amplifier by over 70dB. The gain is adjustable by applying a voltage to the AGC input via an external resistor (R<sub>AGC</sub>), the value of which adjusts the curve of gain reduction versus control voltage (see Figure 4). As the output stage of the amplifier is an open collector the maximum voltage gain is determined by R<sub>L</sub>. With load resistance of 1k $\Omega$  the single ended voltage gain is 45dB and with a load resistance of 50 $\Omega$  the voltage gain is 15dB (20log<sub>10</sub> V<sub>OUT</sub>/V<sub>IN</sub>). Another parameter that depends on the load resistance is the bandwidth: 25MHz for R<sub>L</sub> = 1k $\Omega$ , as compared with 400MHz for R<sub>L</sub> = 50 $\Omega$ . R<sub>L</sub> is chosen to give either the required bandwidth or voltage gain for the circuit.

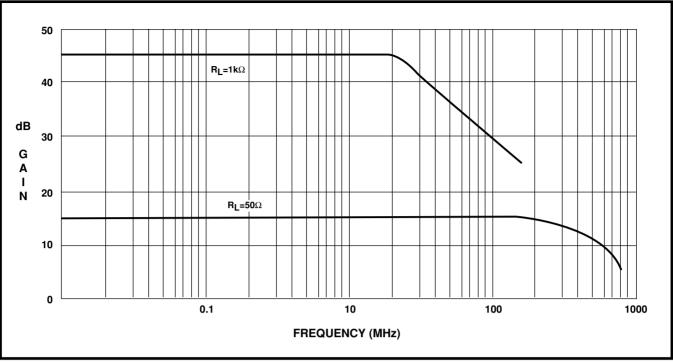

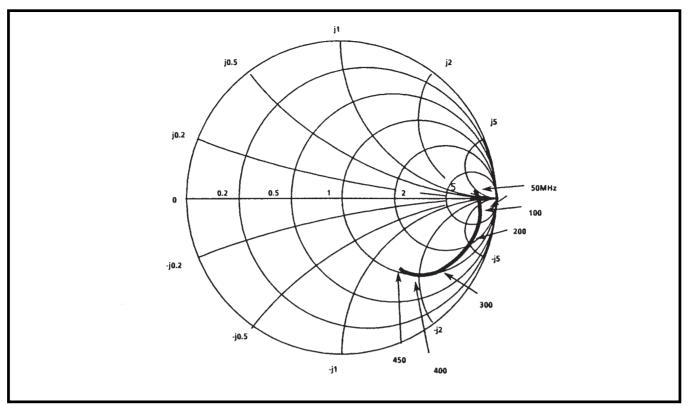

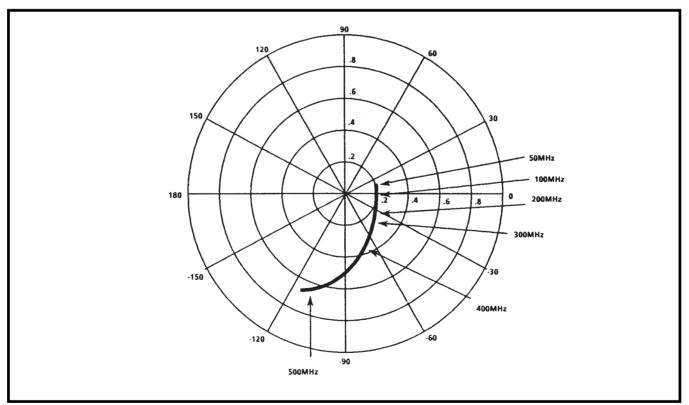

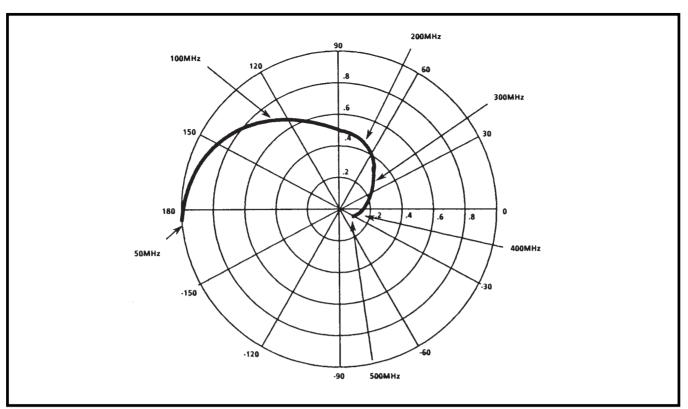

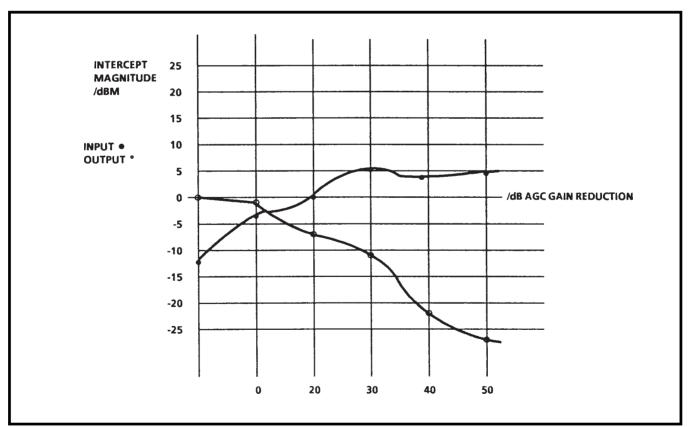

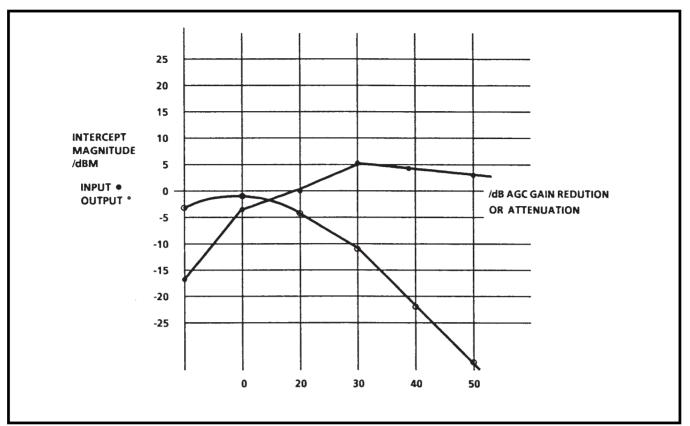

Figure 7 through to 10 show the typical S parameters for the device. Figures 11 and 12 show the typical variation in 3rd order intercept performance with AGC.

In any application, the substrate should be connected to the most negative point in the circuit, usually to the same point as pin 3.

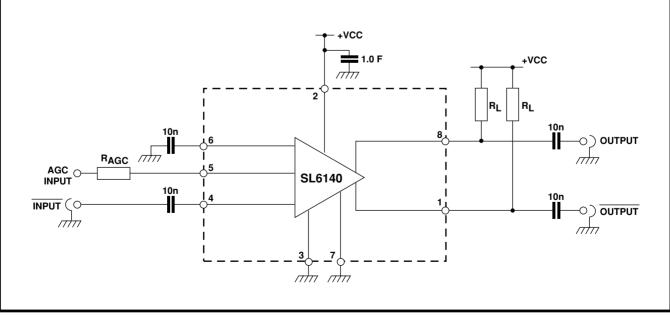

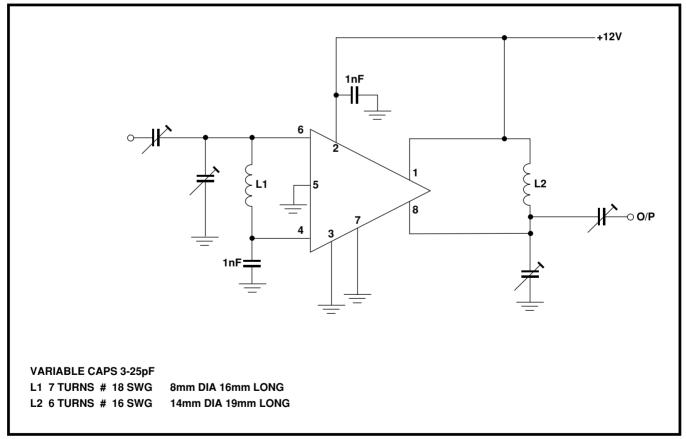

Figure 1 Typical Application

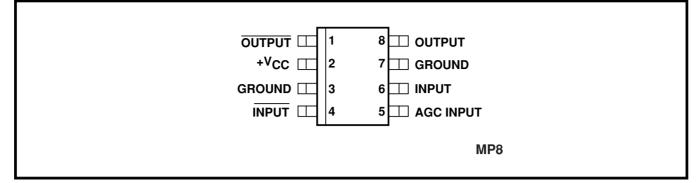

Figure 2 Pin Connections Diagram (top view)

# **Electrical Characteristics**

$T_{amb} = 25^{\circ}C$ ,  $V_{CC} = 12V + 5^{\circ}$ ,  $V_{IN} = 1mV_{RMS}$ , Frequency = 6MHz, Load ( $R_L$ ) = 10KOHms,  $R_{AGC} = 22KOHm$ These characteristics are guaranteed over the following conditions (unless otherwise stated)

| Oberesteristic                                                             | Value Value  |     |                |    |                |                                                                                      |  |

|----------------------------------------------------------------------------|--------------|-----|----------------|----|----------------|--------------------------------------------------------------------------------------|--|

| Characteristic                                                             | Pin          | Min | Min Typ        |    | Units          | Conditions                                                                           |  |

| Supply current                                                             | 5,6,7        |     | 19             | 23 | mA             | No input signal                                                                      |  |

| Output stage current                                                       | 5,6<br>(sum) | 5   | 7              | 9  | mA             | No input signal                                                                      |  |

| Output current matching<br>(magnitude of difference of output<br>currents) | 5,6          |     | 1.0            |    | mA             |                                                                                      |  |

| AGC range                                                                  | 2            | 60  | 75             |    | dB             | See Figure 4 & Note 1<br>(VAGC = 0V to 10V)                                          |  |

| Voltage gain (single ended)                                                | 5,6<br>5,6   | 40  | 45<br>55<br>15 |    | dB<br>dB<br>dB | $R_L = 1k\Omega$ See Figure 5 & Note 1<br>Tuned input and output<br>$R_L = 50\Omega$ |  |

| Bandwidth (-3dB)                                                           | 5,6          |     | 25<br>400      |    | MHz            | RL = 1kΩ See Figure 5<br>RL = 50Ω                                                    |  |

| Maximum output level (single<br>ended)<br>0dB AGC<br>-30dB AGC             | 5,6<br>5,6   |     | 3.5<br>3.5     |    | V p-p<br>V p-p | Note 1<br>R <sub>L</sub> = 1k $\Omega$ . Note 1                                      |  |

| Noise figure                                                               | 5,6          |     | 5              |    | dB             | Test CCT Figure 13                                                                   |  |

Note. 1 Guaranteed but not tested.

#### **Absolute Maximum Ratings**

| Supply voltage, V <sub>CC</sub> | +18V            |

|---------------------------------|-----------------|

| Input voltage (differential)    | +5V             |

| AGC supply                      | V <sub>CC</sub> |

| Storage temperature             | -55°C to +150°Č |

| Operating temperature range     |                 |

| SL6140 MP                       | -40°C to +85°C  |

|                                 | at 200mW        |

| Chip operating temperature      |                 |

| SL6140 MP                       | +150°C          |

|                                 |                 |

## **Thermal Resistance**

| Chip-to-ambie | ent |         |

|---------------|-----|---------|

| SL6140        | MP  | 163°C/W |

| Chip-to-case  |     |         |

| SL6140        | MP  | 57°C/W  |

|               |     |         |

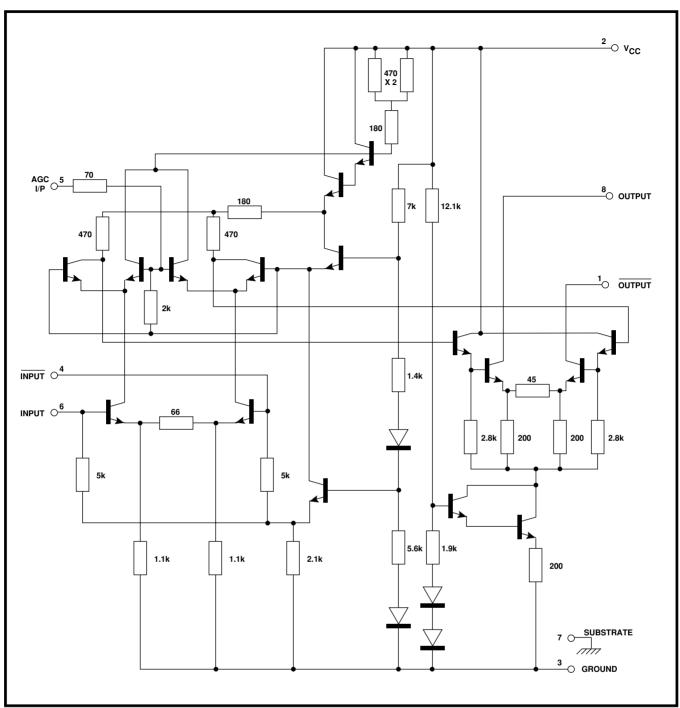

Figure 3 Full Circuit Diagram of SL6140

Figure 5 Max Differential O/P Voltage v. Gain Reduction

Figure 6 Voltage Gain v. Frequency

Figure 7 Input Impedance 50 $\Omega$  System

Figure 8 Output Impedance 50  $\Omega$  System

Figure 9 Reverse Transmission Coefficient S<sub>12</sub> SL6140

Figure 10 Forward Transmission Coefficient S<sub>12</sub> SL6140

Figure 11 3rd Order Intercept Point Against Gain Reduction At 250.0MHz and 254.0MHz

Figure 12 3rd Order Intercept Point Against Gain Reduction At 100.0MHz and 104.0MHz

Figure 13 50MHz Noise Figure Test Circuit

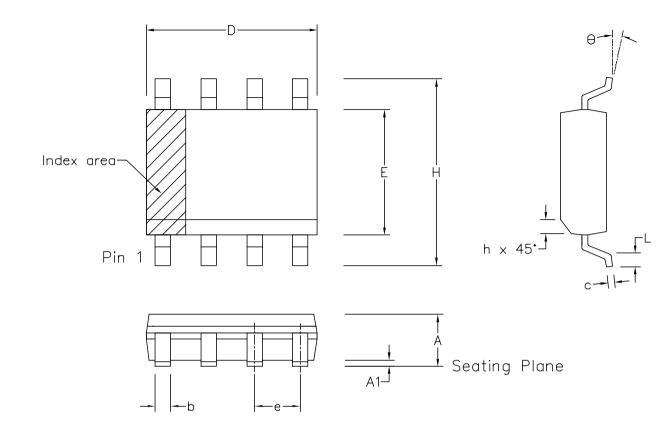

|          | Min  | Max  | Min                     | Max   |  |

|----------|------|------|-------------------------|-------|--|

|          | mm   | mm   | inch                    | inch  |  |

| A        | 1.35 | 1.75 | 0.053                   | 0.069 |  |

| A1       | 0.10 | 0.25 | 0.004                   | 0.010 |  |

| D        | 4.80 | 5.00 | 0.189                   | 0.197 |  |

| Н        | 5.80 | 6.20 | 0.228                   | 0.244 |  |

| E        | 3.80 | 4.00 | 0.150                   | 0.157 |  |

| L        | 0.40 | 1.27 | 0.016                   | 0.050 |  |

| е        | 1.27 | BSC  | 0.050 BSC               |       |  |

| b        | 0.33 | 0.51 | 0.013                   | 0.020 |  |

| С        | 0.19 | 0.25 | 0.008                   | 0.010 |  |

| 0        | ٥    | 8°   | 0°                      | 8°    |  |

|          |      |      | 0 04 0                  |       |  |

| <u>h</u> | 0.25 | 0.50 | 0.010                   | 0.020 |  |

| h        | 0.25 |      | <u>0.010</u><br>eatures | 0.020 |  |

| h<br>N   |      |      | atures                  | 3     |  |

# Notes:

- 1. The chamfer on the body is optional. If it not present, a visual index feature, e.g. a dot, must be located within the cross-hatched area.

- 2. Controlling dimension are in inches.

- Dimension D do not include mould flash, protusion or gate burrs. These shall not exceed 0.006" per side.

Dimension E1 do not include inter-lead flash or protusion. These shall not exceed 0.010" per side.

Dimension b does not include dambar protusion/intrusion. Allowable dambar protusion shall be 0.004"

- total in excess of b dimension.

| © Mitel  |        |         |         |        |  |       |               | ORIGINATING SITE: SWINDON                                                  |

|----------|--------|---------|---------|--------|--|-------|---------------|----------------------------------------------------------------------------|

| ISSUE    | 1      | 2       | 3       | 4      |  |       |               | Title: Package Outline Drawing for<br>8 Ids SOIC(N)-0.150" Body Width (MP) |

| ACN      | 006745 | 201936  | 202595  | 203705 |  | MITEL | SEMICONDUCTOR | 8 Ids SOIC(N)-0.150 Body Width (MP)                                        |

| DATE     | 5APR95 | 27FEB97 | 12JUN97 | 9DEC97 |  |       |               | Drawing Number                                                             |

| APPROVED |        |         |         |        |  |       |               | GPD00010                                                                   |

http://www.mitelsemi.com

#### World Headquarters - Canada

Tel: +1 (613) 592 2122 Fax: +1 (613) 592 6909

#### North America

Tel: +1 (770) 486 0194 Fax: +1 (770) 631 8213

#### Asia/Pacific

Tel: +65 333 6193 Fax: +65 333 6192

#### Europe, Middle East, and Africa (EMEA) Tel: +44 (0) 1793 518528 Fax: +44 (0) 1793 518581

Information relating to products and services furnished herein by Mitel Corporation or its subsidiaries (collectively "Mitel") is believed to be reliable. However, Mitel assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Mitel or licensed from third parties by Mitel, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Mitel, or non-Mitel furnished goods or services may infringe patents or other intellectual property rights owned by Mitel.

This publication is issued to provide information only and (unless agreed by Mitel in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Mitel without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or services (Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Mitel's conditions of sale which are available on request.

M Mitel (design) and ST-BUS are registered trademarks of MITEL Corporation Mitel Semiconductor is an ISO 9001 Registered Company Copyright 1999 MITEL Corporation All Rights Reserved Printed in CANADA

TECHNICAL DOCUMENTATION - NOT FOR RESALE